| D        | Page 1 of 8    |

|----------|----------------|

| Doc. No. | d Confidential |

**Approvals:**

Vin Healy

**Management Representative**

Rich Guerin & Jay Little

**Department Manager / Process Owner**

# **Revision History**

| Date       | Change /<br>ECO Notice | <b>Change Description</b>                                                                                                                  |  |  |  |  |

|------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 04/24/2014 | А                      | Initial Draft                                                                                                                              |  |  |  |  |

| 06/05/2020 | 12586                  | Updated equipment board sizes and component spacing, added DWI-009-002-48 under References. Changed the doc # from DQP-022-003 to DQP-041. |  |  |  |  |

| 4/27/2021  | 13539                  | Change 3.1 to updated form number. Inserted sections 6.28 and 6.29 for test.                                                               |  |  |  |  |

| 3/24/2025  | 17368                  | Wording and in section 6.28 has been updated to match current flying probe specs.                                                          |  |  |  |  |

| Design for Manufacturability Guidelines | Page 2 of 8 |

|-----------------------------------------|-------------|

|-----------------------------------------|-------------|

| Doc. No. | DQP-041 | Revision | D | Proprietary and Confidential |

|----------|---------|----------|---|------------------------------|

|----------|---------|----------|---|------------------------------|

#### 1.0 **Purpose:**

1.1 To define the methods utilized for reviewing the manufacturability of new designs to insure potential issues are resolved before the initial build which will save time and improve product quality.

#### 2.0 Scope:

2.1 This procedure is applicable to all new assemblies manufactured at Distron.

### 3.0 **Applicable Documents:**

- 3.1 New Product Risk Mitigation Analysis (DF-024-004)

- 3.2 PCB Fiducial and General Mfg Requirements Procedure (DWI-009-002-48)

### 4.0 **Definitions:**

- 4.1 PCB - Printed Circuit Board

- 4.2 SMD – Surface Mount Device

- 4.3 BGA - Ball Grid Array

### 5.0 **Responsibilities:**

- It is the responsibility of the Manufacturing and Management Representatives and/or 5.1 designee to ensure the requirements within this procedure are followed and for training applicable personnel.

- 5.2 It is the responsibility of the Engineering Department to ensure all new designs are reviewed per this procedure.

### 6.0 **Procedure:**

### 6.1 **Fiducials:**

- 6.1.1 Distron's automated equipment utilizes fiducials as reference points that are required for accurate assembly of components on PCBs.

- 6.1.2 Fiducials are an artwork feature created within the PCB conductive pattern to provide a measureable point for component mounting and are utilized by the automated equipment's imaging system as a point of reference to locate a position of all PCB land patterns.

- Fiducials are placed on the top and bottom copper layer. They should not be 6.1.3 placed on the mask or silkscreen layer because the layers are not as precise as the copper layer.

- 6.1.4 Board fiducials are used to locate the position of all PCB land patterns.

- 6.1.5 Panel Fiducials are used to locate the rails or perimeter of a multi-up panel.

- 6.1.6 Board and panel fiducials are required.

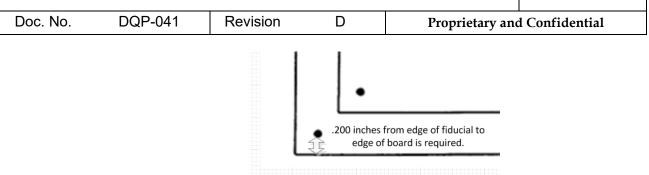

- 6.1.7 Fiducial spacing is from the edge of the board to the edge of the fiducial and must be at least .200 inches as shown below.

Note: Reference the PCB Fiducial and General Mfg Requirements Procedure (DWI-009-002-48) for additional information.

# **Design for Manufacturability Guidelines**

# 6.2 **Board Sizes:**

The table below lists the minimum and maximum board sizes that will fit Distron's assembly equipment.

| Equipment                               | Min. Length and Width board<br>size (inches | Max. Length and Width board size           |

|-----------------------------------------|---------------------------------------------|--------------------------------------------|

| Electrovert Wave Solder Machine         | 2″ width                                    | 16" conveyor width /14"<br>soldering width |

| Pillarhouse Selective Solder<br>Machine | 4"x4"                                       | 20"x18"                                    |

| Juki Selective Solder Machine           | .79″x .79″                                  | 18"x18"                                    |

### SMT Equipment Board Sizes

| Equipment                  | Min. Length and Width board<br>size (inches)* | Max. Length and Width board<br>size (inches)* |

|----------------------------|-----------------------------------------------|-----------------------------------------------|

| _ · ·                      | · · ·                                         | . ,                                           |

| Dek 03iX Screen Printers   | 1.96"x1.59"                                   | 20"x20"                                       |

| Vitech Pi Paste Inspection | 2"x2"                                         | 21"x21"                                       |

| Equipment                  |                                               |                                               |

| Mycronic Pick and Place    | 2.7"x2"                                       | 22"x20"                                       |

| Equipment                  |                                               |                                               |

| Heller 1809 Reflow Ovens   | 2" (width)                                    | 18"-20" (width)                               |

| Yestech AOI Inspection     | 2″x2″                                         | 22"x20"                                       |

| Equipment                  |                                               |                                               |

| Vitech 3D AOI Inspection   | 2"x2"                                         | 21"x24"                                       |

| Equipment                  |                                               |                                               |

| Dage XRAY Equipment        | na                                            | 29"x22"/inspect area 20"x17.5"                |

\*Minimum and maximum board size may be affected by stand-alone or in-line configuration.

# 6.3 **Polarity Marks:**

All polarized parts should have polarity marks that are in the silkscreen layer or the copper layer. The marks should be visible after the components are installed for inspection purposes.

# 6.4 **Diode Orientation**

- 6.4.1 Clearly identify the orientation of the various types of diodes.

- 6.4.2 It is preferred to use a "C" for cathode side or "A" for anode side or use the schematic diode symbol.

- 6.4.3 Ensure the diode marks are visible after installing the components.

# 6.5 Lead to Hole Ratio:

### 6.5.1 **Through Hole Components:**

| D        | esign f                                                                                                  | for Ma    | nufacturab                               | oility Gui      | delines                                             | Page 4 of 8           |  |  |

|----------|----------------------------------------------------------------------------------------------------------|-----------|------------------------------------------|-----------------|-----------------------------------------------------|-----------------------|--|--|

| Doc. No. | DQP                                                                                                      | 2-041     | Revision                                 | D               | Proprietary and                                     | l Confidential        |  |  |

|          | 6.5.1.1 Adequate space within the hole is required to ensure fill of solder and for automated insertion. |           |                                          |                 |                                                     |                       |  |  |

|          |                                                                                                          |           | The finished hole<br>lead.               | e size should   | be .019" larger than (>)                            | ) the diameter of the |  |  |

|          |                                                                                                          |           | The diameter for corners of the lea      | •               | would be the distance a                             | across diagonal       |  |  |

| 6.6      | Tabs/l                                                                                                   | Mousebit  | es:                                      |                 |                                                     |                       |  |  |

|          | 6.6.1                                                                                                    | Tabs are  | e used to connect                        | PCBs within     | a routed panel.                                     |                       |  |  |

|          | 6.6.2                                                                                                    |           | oites are the holes<br>out of the panel. | within the ta   | bs that allow the board                             | to be cleanly         |  |  |

|          | 6.6.3                                                                                                    | General   | guidelines:                              |                 |                                                     |                       |  |  |

|          |                                                                                                          |           |                                          |                 | e .050" wide tabs place<br>n the center of PCB edg  | •                     |  |  |

|          |                                                                                                          | 6.6.3.2   | Larger and thicke                        | er boards will  | require wider tabs.                                 |                       |  |  |

|          |                                                                                                          | 6.6.3.3   | Internal copper w                        | vill need to be | e relieved from the PCE                             | B edge.               |  |  |

|          |                                                                                                          |           | Keep traces away<br>during separatior    |                 | ouse bite holes to preve                            | nt any damage         |  |  |

|          |                                                                                                          |           |                                          | -               | , the opening size shou<br>hibbler tool to cut each |                       |  |  |

|          | 6.6.4                                                                                                    | Distron   | can assist with pa                       | anel design if  | needed to ensure the p                              | rocess is optimized.  |  |  |

| 6.7      | Panel                                                                                                    | Breakaw   | ays:                                     |                 |                                                     |                       |  |  |

|          | 6.7.1                                                                                                    | Panel br  | eakaways may in                          | terfere with o  | overhanging componen                                | ts.                   |  |  |

|          | 6.7.2                                                                                                    | Panel de  | esign should allow                       | w for connect   | ors that overhang the b                             | oard edge.            |  |  |

|          | 6.7.3                                                                                                    |           | ouse bites should<br>during depenaliz    |                 | l under the connectors t                            | o prevent potential   |  |  |

|          | 6.7.4                                                                                                    |           | oites are not locate                     |                 | ated within the Gerber<br>nnector or near a trace   |                       |  |  |

|          |                                                                                                          | Note: T   | This information i                       | s also helpful  | when V-scoring is use                               | ed.                   |  |  |

| 6.8      | Comp                                                                                                     | onents To | oo Close to the P                        | CB Edge:        |                                                     |                       |  |  |

|          | 6.8.1                                                                                                    |           | cturing equipmen<br>PCB effectively.     |                 | echanisms require un-o                              | obstructed room to    |  |  |

|          | 6.8.2                                                                                                    |           | components, suc<br>g when they are p     |                 | capacitors and resistor<br>se to the edge.          | s, are at risk of     |  |  |

6.8.3 Components should be placed 6.35 mm from the PCB edge.

Note: Parallel to the PCB edge is better to prevent potential damage during depanelization.

6.9 Cleaning:

| De       | esign f | or Ma                  | nufactural                            | oility Gu      | uidelines                                                                | Page 5 of 8           |

|----------|---------|------------------------|---------------------------------------|----------------|--------------------------------------------------------------------------|-----------------------|

| Doc. No. | DQP     | -041                   | Revision                              | D              | Proprietary an                                                           | d Confidential        |

|          | 6.9.1   | Sealed of              |                                       |                | water-soluble fluxes afte<br>utilize a No Clean Solde                    |                       |

|          |         | I                      |                                       | nple, switch   | re not able to withstand<br>les, speakers, batteries an<br>ing process.  |                       |

|          | 6.9.2   |                        | nents that are not ncreases cost.     | compatible     | with cleaning may requi                                                  | re manual solderin    |

|          | 6.9.3   |                        | embly drawing shaled components.      | nould note a   | ny components that can                                                   | not be washed such    |

|          | 6.9.4   |                        |                                       |                | baked after wash to rem<br>by the customer.                              | ove any residual      |

| 6.10     | Vias:   |                        |                                       |                |                                                                          |                       |

|          | 6.10.1  | insuffic               |                                       | is also poter  | rom the component sold<br>ntial that a visual inspect<br>ls if possible. |                       |

|          | 6.10.2  | Allow a pad.           | .015" of solder r                     | nask if utiliz | zing solder mask to sepa                                                 | rate the via from the |

|          | 6.10.3  | Filled v               | ias may also be u                     | sed to preve   | ent solder drain.                                                        |                       |

|          | 6.10.4  |                        |                                       |                | IPC recommends unifor<br>not be achievable with up                       |                       |

|          | 6.10.5  |                        |                                       | -              | red. Avoid using differe<br>terminations will be acl                     | -                     |

|          | 6.10.6  |                        | vias on the solde<br>solder bridging. | r side shoul   | d be covered with solder                                                 | mask to reduce th     |

| 6.11     | Solder  | Mask:                  |                                       |                |                                                                          |                       |

|          | 6.11.1  | Solder I               | Mask between fin                      | e pitch pade   | s is recommended to red                                                  | uce solder bridges.   |

|          |         |                        |                                       | -              | st a .004" wide to fit the ith the PCB fabricator or                     |                       |

|          | 6.11.2  |                        | nask between pac<br>and flux entrapm  |                | e components can contri                                                  | bute to drawbridge    |

|          |         |                        |                                       |                | ove the Solder Mask bet<br>are no traces between th                      | -                     |

| 6.12     | NSMD    | or SMD                 | o pads for BGAs                       |                |                                                                          |                       |

|          |         | older Mas<br>joints on | ,                                     | D) pads are    | preferred in order to have                                               | ve uniform sized      |

| 6.13     | Lead H  | Free Sold              | er Balls on BGA                       | s in a Lead    | led design:                                                              |                       |

|          | Notify  | Distron i              | f Lead Free devi                      | ces will be    | utilized on a Tin Lead de                                                | esign.                |

Note: Reflow profile adjustments will be needed.

6.14 **Thermal Relief:**

| De       | esign f | or Ma               | anufacturab                                 | oility Gui      | delines                                          | Page 6 of 8            |

|----------|---------|---------------------|---------------------------------------------|-----------------|--------------------------------------------------|------------------------|

| Doc. No. | DQP     | -041                | Revision                                    | D               | Proprietary and                                  | d Confidential         |

|          | 6.14.1  | Solder<br>require   | · ·                                         | h hole compo    | nents is required to me                          | eet IPC                |

|          | 6.14.2  | solder              | •                                           | n hole parts; e | reach the temperature t<br>specially on heavy Co | <b>e</b>               |

|          | 6.14.3  | Ensure              | adequate thermal                            | reliefs exist o | n the design.                                    |                        |

| 6.15     | Wire N  | Aodifica            | ations:                                     |                 |                                                  |                        |

|          |         |                     | tions are usually lange into the PCB.       | bor intensive.  | It may be more reliab                            | ble and less costly to |

| 6.16     | BGA (   | Compon              | ent Spacing:                                |                 |                                                  |                        |

|          |         | · ·                 | g is recommended<br>es or replacement i     |                 | s to allow enough roor                           | n for hot air rework   |

| 6.17     | Selecti | ve Solde            | ering Spacing:                              |                 |                                                  |                        |

|          | A .1" s | pacing is           | s preferred betwee                          | n through-hol   | le lead and SMT comp                             | onents.                |

| 6.18     | No Cle  | an Sold             | er & Flux Residu                            | le:             |                                                  |                        |

|          | 6.18.1  | micro I             |                                             | •               | ended on some compor<br>difficulty in removing   |                        |

|          | 6.18.2  | Flux re             | sidue may affect h                          | nigh impedance  | e designs.                                       |                        |

|          | 6.18.3  | Ensure<br>chemis    |                                             | manufacturin    | g is acceptable if utiliz                        | ing No Clean           |

|          | 6.18.4  | Ensure              | the preferred sold                          | er chemistry i  | is identified.                                   |                        |

| 6.19     | Trace   | Cuts:               |                                             |                 |                                                  |                        |

|          | •       |                     | cost effective to r<br>cuts since it is a m |                 | rd and change the PCB                            | rather than            |

| 6.20     | SMT v   | 's Throu            | igh-Hole:                                   |                 |                                                  |                        |

|          | 6.20.1  |                     | n recommends SM<br>bly steps will add c     |                 | s wherever possible. T<br>embly.                 | Through-hole           |

|          | 6.20.2  |                     | gate if there are SM<br>ential cost savings |                 | es if a design has a few                         | through-hole parts     |

| 6.21     | Lead I  | Lengths             | of Through-Hole                             | Components      | 5:                                               |                        |

|          | 6.21.1  | Identify<br>require |                                             | length require  | ements or other compo                            | nent height            |

|          | 6.21.2  | Lead le             | ength requirements                          | s below .040"   | add labor cost.                                  |                        |

|          | 6.21.3  | Lead le             | ength requirements                          | s above .15" o  | or 4.00mm add labor co                           | ost.                   |

| 6.22     | PCB F   | inish               |                                             |                 |                                                  |                        |

Electroless Nickel Immersion Gold per IPC-4552 is the preferred finish as it provides flat pads and has a long storage life.

# 6.23 **PCB Fabrication**

# Design for Manufacturability Guidelines

Doc. No.DQP-041RevisionDProprietary and Confidential

- 6.23.1 Define the laminate stack up clearly.

- 6.23.2 Determine which board fabricator is capable of building the board based on the following characteristics:

- Minimum trace width

- Minimum distance between traces

- Smallest hole diameter

# 6.24 Workmanship Class:

Identify the assembly workmanship class (Class 1,2 or 3) and any other build standards required on assembly documentation.

# 6.25 **PCB Laminate Specification:**

- 6.25.1 Identify the PCB laminate material specifications in the PCB fabrication drawing.

- 6.25.2 For Lead Free/ROHS assemblies, the laminate must have a glass transition temperature (Tg) of greater than or equal to (≥) 175°C.

# 6.26 Labelling and Traceability

- 6.26.1 Identify product labelling and traceability requirements on assembly documentation.

- 6.26.2 It is recommended to include an outline box in the silkscreen layer for the label.

# 6.27 **Torque Specifications:**

Identify torque requirements in assembly documentation.

# 6.28 **Probe and Fixture Guidelines:**

- Test Pads/Vias on all Nets.

- Index Tolerance + 0.002 inches Datum to Test Pad.

- Two Tooling Holes on UUT + 0.002 Tolerance between them.

- Tooling Hole Diameters + 0.0031 / -0.000 inches.

- Test Pad / Via Pad Size 0.035 to 0.040 inches.

- Test Pad / Via Pad Separation 0.015 inches.

- Test Pad Center to Center Spacing.

| Priority | Preferred | Acceptable |

|----------|-----------|------------|

| 1        | 0.100"    | 0.085"     |

| 2        | 0.075"    | 0.070"     |

| 3        | 0.050"    | 0.050"     |

- Test Pads can be located on both sides of board.

- Keep Component Height on test side less than 1.0" if possible.

- No components or test pads closer than 0.125" from edge of UUT.

- No resist on test pads.

- Fill through hole vias with solder

- No probing of component leads.

- Distribute test pads evenly over PC Board.

- Provide clearance space for fixture push finger.

- Minimize fixture changes when redesigning boards

| D        | Page 8 of 8    |  |  |  |  |  |  |

|----------|----------------|--|--|--|--|--|--|

| Doc. No. | d Confidential |  |  |  |  |  |  |

|          |                |  |  |  |  |  |  |

# 6.29 Electrical Design Guidelines:

- Provide Test Access to All Electrical Nodes.

- Place Test Pads as close as possible to signal source.

- Include 2 Test Pads on each Electrical Node tied to Critical Low Impedance.

- **DO NOT** rely on edge connector, circuit traces, or SMT Device Pads for Test Points.

- Use pull up and fill down resistors for control of IC Control Lines.

- Include Test Pads for unused Device Pins.

- Includes method to disable Clock Sources.

- Provide Disable methods for ALL Programmable Logic Devices.

- Include Pull-up loads on all open device inputs.

- Provide disable methods for all Bussed Devices, High Current Devices, and Devices tied to Flash, Rams, EEProms, and D/A Converter.

- Include circuitry to Disable Feedback Loops.

- Use Devices with short Initialization Times.

- Provide Vectors for all ASIC and Custom Devices

- In using Vectorless test don't use devices with heat sink or ground plans on top.

- Supply Documentation for Device Logic Function.

- Use IEEE 1149 Boundary Scan and 1149.4 Analog and Mixed Signal compatible devices.

- Isolate Power On Reset Circuits from other digital devices.

- Place Test Pads and Power and Ground Nodes as close as possible to each Digital Devices under test.

- Use multiple test pads on power and ground connections.

- Allow for Battery Isolation during In-Circuit Test.

- Buffer Test Pads to Analog and Mixed Signal Devices.

- Keep In-Circuit Testing in mind when implementing Engineering Changes.

# 6.30 **Regulatory Requirements:**

Identify all regulatory requirements.

# 6.31 Packaging Requirements:

Identify any special final packaging requirements.

# 6.32 Design Checklist

Utilize the New Product Risk Mitigation Analysis (DF-024-004) to confirm the assembly is manufacturable which will ensure a robust manufacturing process and product reliability.

# 7.0 Records:

7.1 Keep records per the Records Control Procedure (DQP-016).

End of Document